Wichtigste Erkenntnisse

- Eine gründliche Vorbereitung gibt den Integrationsteams die Gewissheit, dass sich die Modelle nach dem Anschluss an die Hardware konsistent verhalten, wodurch kostspielige Überraschungen und Verzögerungen vermieden werden.

- Präzise physikalisch basierte Komponenten bilden die Grundlage für Hardwaretests, die zeigen, wie Systeme unter Belastung reagieren.

- Echtzeit-Optimierungsschritte helfen Modellen dabei, feste Ausführungsfristen einzuhalten, sodass Sie Hardwaretests ohne Überschreitungen oder Instabilitäten durchführen können.

- Eine frühzeitige Schnittstellenplanung minimiert Nacharbeiten, indem sichergestellt wird, dass alle Signale, Kanäle, Einheiten und Skalierungen aufeinander abgestimmt sind, bevor das System auf den Prüfstand kommt.

- Gründliche Überprüfungsverfahren bieten Teams einen strukturierten Weg, um Verhalten, Zeitplanung und Annahmen zu validieren, bevor sie mit Hardware-Tests beginnen.

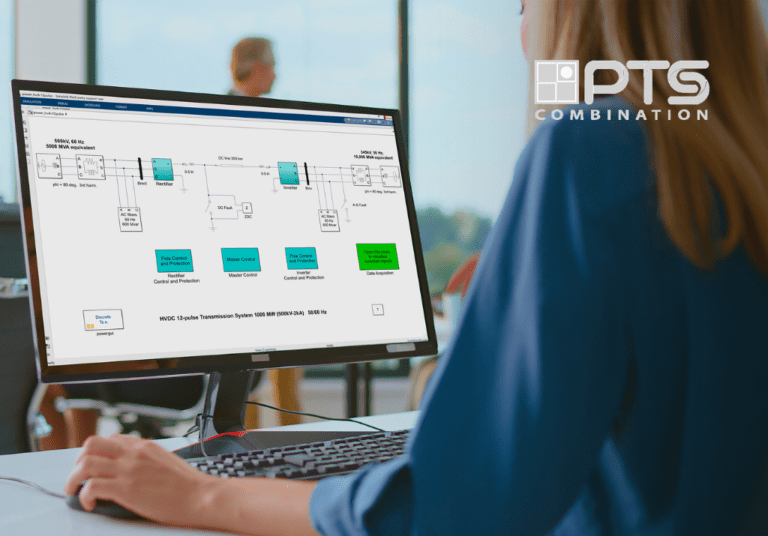

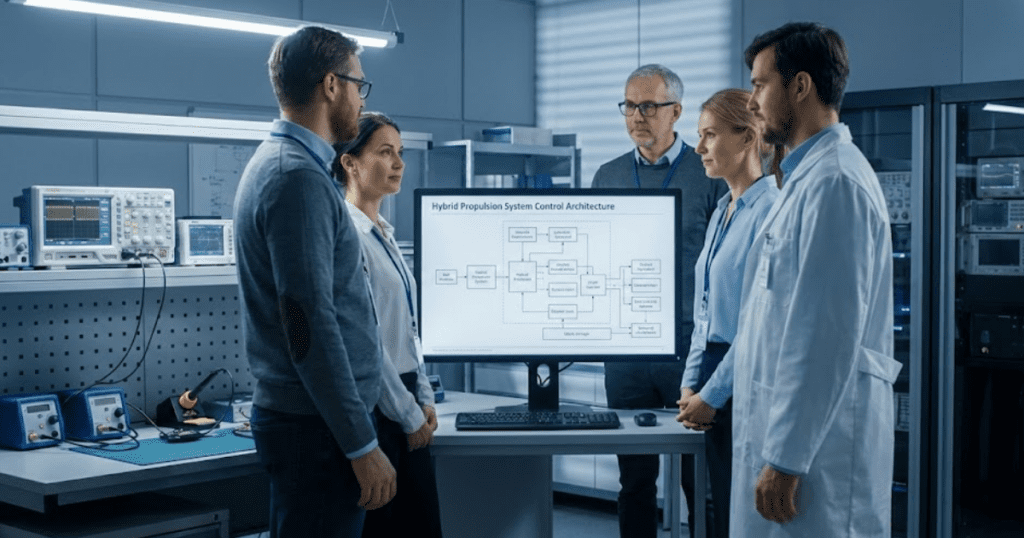

Ein einziges fehlerhaftes Simulationsmodell kann einen gesamten Hardware-Testplan zum Scheitern bringen. Integrationsteams stellen häufig fest, dass Modelle, die auf einem Desktop einwandfrei laufen, unter Echtzeitbedingungen unvorhersehbar reagieren. Wir haben erlebt, dass Projekte ins Stocken geraten sind, wenn ein Controller-Modell plötzlich die Timing-Vorgaben auf der Zielhardware nicht mehr erfüllen konnte oder wenn die Signalschnittstellen nicht mit dem physischen Prüfstand übereinstimmten. Ohne gründliche Vorbereitung liefern Hardware-in-the-Loop-Tests (HIL) unzuverlässige Ergebnisse oder führen sogar zu kritischen Ausfällen. Moderne Echtzeitlabore können beispielsweise komplexe Stromnetze mit rund 10.000 Knoten simulieren, was bedeutet, dass selbst ein kleiner Modellierungsfehler eine Kettenreaktion im gesamten System auslösen kann. Eine rigorose Modellvorbereitung behebt diese Probleme: Sie überprüft die Genauigkeit, optimiert die Leistung und kontrolliert die Schnittstellen im Voraus. Der Lohn dafür sind sicherere Tests, schnellere Iterationen und ein höheres Maß an Vertrauen in die Ergebnisse.

Genaue Modelle verhindern Überraschungen beim Hardwaretest

Eine präzise, physikalisch fundierte Modellierung ist die Grundlage für zuverlässige Hardwaretests. Wenn ein Modell zu stark vereinfachte Komponenten oder feste Signale verwendet, kann sein Verhalten vom tatsächlich getesteten System abweichen. Ingenieure sollten sicherstellen, dass jede Komponente auf der Physik und den Parametern des realen Systems basiert. Wenn beispielsweise Verluste in einem Stromrichter vernachlässigt oder Sensorantworten idealisiert werden, kann dies zu Fehlanpassungen führen, die nur auftreten, wenn das Modell mit realer Hardware verbunden ist. Diese Art von Diskrepanz zwingt Teams dazu, Probleme außerhalb der Simulation zu verfolgen, was wertvolle Projektzeit kostet.

Beispielsweise können Echtzeitlabore wie der Netzsimulator von Oak Ridge etwa 10.000 Knoten verarbeiten, und eine Open-Source-Plattform simulierte sogar 24.000 Elektronen in Echtzeit. Ein solcher Umfang macht deutlich, dass sich bei großen Simulationen selbst kleine Fehler vervielfachen können. Teams sollten Modelle anhand von Messungen kalibrieren und das Verhalten unter allen zu erwartenden Bedingungen validieren, damit die Simulation die Realität zuverlässig widerspiegelt. Wenn jede Komponente genau und transparent ist, können Ingenieure Parameter spontan anpassen und darauf vertrauen, dass Änderungen zu aussagekräftigen Ergebnissen führen.

„Teams sollten Modelle anhand von Messungen kalibrieren und das Verhalten unter allen zu erwartenden Bedingungen validieren, damit die Simulation die Realität zuverlässig widerspiegelt.“

Echtzeitleistung erfordert ein optimiertes Modell.

Selbst ein genaues Modell versagt, wenn es nicht schnell genug in Echtzeit ausgeführt werden kann. Ingenieure müssen Modelle so optimieren, dass jede Berechnung mit der Hardware-Taktfrequenz Schritt hält. Zu den gängigen Strategien gehören die Verwendung von Solvern mit festen Schritten und synchronen Subsystemen, das Zusammenführen oder Abflachen hierarchischer Blöcke sowie das Entfernen oder Vereinfachen rechenintensiver Elemente. Beispielsweise könnte ein Multi-Domain-Konvertermodell die elektrische Physik in Schritten von 10 μs und thermische Effekte in Schritten von 100 μs ausführen, was eine sorgfältige Wahl des Timings erfordert.

- Löser und Schrittweite: Legen Sie den Löser-Typ und den Zeitschritt so fest, dass sie der Echtzeit-Hardware-Rate entsprechen, um eine deterministische Ausführung zu gewährleisten und Unsicherheiten aufgrund variabler Schritte zu vermeiden.

- Modelle vereinfachen: Entfernen Sie Protokollierungsschemata, Diagnoseblöcke und alle algebraischen Schleifen oder seltenen Funktionen, die die Ausführung verlangsamen.

- Subsysteme vereinfachen und optimieren: Kaskadierte Blöcke zusammenführen und effiziente Optionen zur Codegenerierung nutzen, um den Rechenaufwand zu reduzieren.

- Datentypen und Festkomma: Wählen Sie Datentypen (z. B. Festkomma), die für das Echtzeitziel geeignet sind und kostspielige Typkonvertierungen minimieren.

- Codegenerierung und Bereitstellung: Generieren Sie optimierten C/HDL-Code für die Echtzeitplattform, kompilieren Sie ihn und beheben Sie alle Probleme bei der Codegenerierung vor dem Test.

- Schlanke Signalpfade: Nehmen Sie nur die notwendigen Signale und Berechnungen in die Ausführungsschleife auf, um die Last zu reduzieren und das Timing einzuhalten.

Diese Schritte verwandeln ein Entwurfsmodell in ein Modell, das Echtzeitanforderungen erfüllt. Das Ergebnis sind weniger Terminüberschreitungen und wiederholbare Ausführungszeiten. Insgesamt sorgen optimierte Modelle dafür, dass die Hardware jeden Schritt rechtzeitig berechnen kann, wodurch numerische Instabilitäten und Überschreitungen vermieden werden.

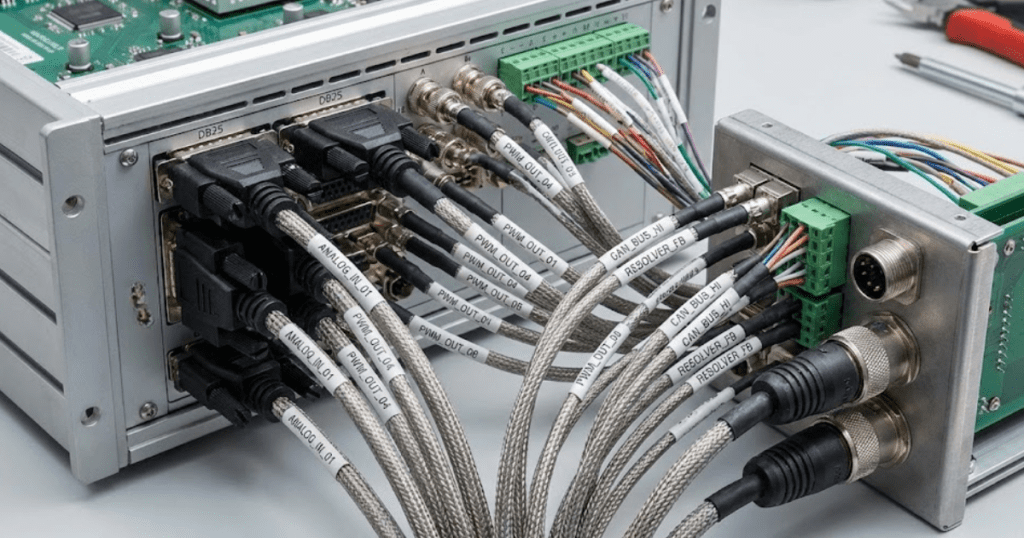

Frühzeitige Schnittstellenplanung verhindert Integrationsprobleme

Hardware-Tests schlagen oft aufgrund von nicht übereinstimmenden Signalen oder übersehenen E/A-Anforderungen fehl. Zu Beginn des Projekts sollten die Teams jede Schnittstelle zwischen dem Modell und der Testausrüstung planen. Das bedeutet, dass vor dem Aufbau der HIL-Konfiguration jeder Eingangs- und Ausgangskanal, seine Einheiten, sein Bereich und der erwartete Datentyp definiert werden müssen. Durch die frühzeitige Festlegung dieser Schnittstellenspezifikationen lassen sich Überraschungen wie ein an den falschen Verstärker angeschlossenes Spannungssignal oder eine zeitliche Fehlanpassung auf einem Kommunikationsbus vermeiden. Es ist hilfreich, von Anfang an eine Dokumentation aller Kanäle und Signalzuordnungen zu erstellen.

Die Teams überprüfen außerdem die Einheitlichkeit der Einheiten und Skalierungen. Sie stellen sicher, dass jedes Modellsignal die gleichen Einheiten verwendet, die die Hardware erwartet, und dass digitale Formate (wie ADC-Bitbereiche oder Kommunikationsprotokolle) übereinstimmen. Beispielsweise können durch die Zuordnung von Simulink-Blockausgängen zu Hardwarekanälen und deren Überprüfung mit einfachen Testsignalen Abgleichprobleme frühzeitig erkannt werden. Die Dokumentation von Kanalzuweisungen, erwarteten Wertebereichen und Anschlusszuordnungen wird zu einer konkreten Checkliste für die Integrationsphase. In der Praxis spart die parallele Behandlung der Schnittstelleneinrichtung und der Modellierung Tage an Debugging-Zeit. Zum Zeitpunkt der Integration können die Teams das Modell dann sicher anschließen und sich auf die Funktionalität konzentrieren, anstatt Unstimmigkeiten zu suchen.

Gründliche Modellprüfungen sind die letzte Kontrolle vor den Hardwaretests.

„Ein einziges fehlerhaftes Simulationsmodell kann einen gesamten Hardware-Testplan zum Scheitern bringen.“

Verhalten der Komponente überprüfen

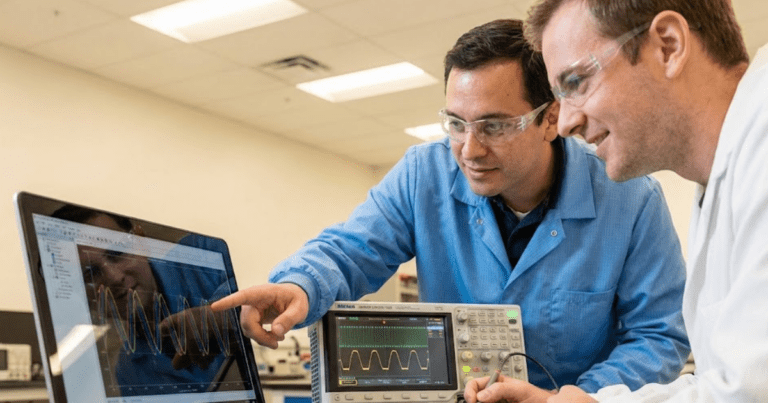

Ingenieure überprüfen jede Komponente doppelt, indem sie sie nach Möglichkeit isoliert testen. Beispielsweise könnte man einen simulierten Sensor mit einer bekannten Eingangswellenform ansteuern und sicherstellen, dass die Ausgabe mit den theoretischen oder experimentellen Daten übereinstimmt. Durch die Überprüfung von Grenzfällen und Sensorrauschreaktionen lassen sich Modellierungsprobleme frühzeitig erkennen. Auch benutzerdefinierter Code und Nachschlagetabellen werden hier überprüft, um sicherzustellen, dass jeder Block wie vorgesehen funktioniert und seine Ausgaben den Erwartungen entsprechen. Durch diese Tests auf Komponentenebene werden Fehler im Kontext erkannt und beeinträchtigen größere Tests nicht.

Test-Randfallszenarien

Eine gründliche Überprüfung umfasst auch abnormale Bedingungen. Ingenieure simulieren Fehlerszenarien, extreme Eingaben und Randbedingungen, um zu sehen, ob die Modellreaktion realistisch bleibt. Beispielsweise können sie einen plötzlichen Stromausfall oder einen Sensor-Nullwert simulieren, um die Schutzlogik und die Robustheit der Steuerung zu überprüfen. Das Erkennen von unrealistischem oder instabilem Verhalten in diesen Simulationen verhindert Überraschungen während der tatsächlichen Tests. Diese Stresstests dienen als Plausibilitätsprüfung und stellen sicher, dass versteckte Annahmen im Modell unter extremen Bedingungen nicht zusammenbrechen.

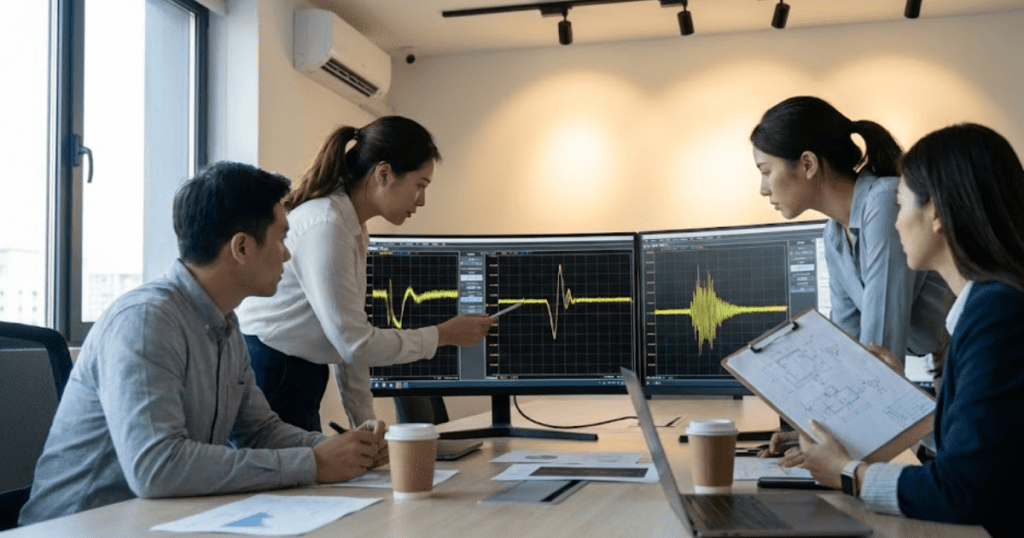

Leistung und Timing überprüfen

Während der Überprüfung bestätigen die Teams, dass die Ausführung des Modells auf der Zielhardware innerhalb akzeptabler Grenzen liegt. Dazu gehört auch die Überprüfung, ob das Modell die vorgesehene Abtastzeit ohne Überschreitungen einhält. Ein einfacher Kompilier- und Ausführungstest auf der Echtzeitplattform zeigt, ob eine Aufgabe zu lange dauert. Die Ingenieure achten auf verpasste Fristen oder Solver-Warnungen und stellen sicher, dass alle Hardware-I/Os (wie PWM- oder ADC-Blöcke) das richtige Timing verwenden. Das Aufdecken solcher Engpässe jetzt vermeidet spätere Integrationsprobleme auf dem realen Prüfstand.

Dokumentieren Sie Annahmen und Schnittstellen.

Schließlich umfasst eine Modellüberprüfung auch die Dokumentation. Die Ingenieure fassen alle wichtigen Annahmen, Parameterwerte und Schnittstellenzuordnungen zusammen. Eine zusammenfassende Liste der Zustandsvariablen, Anfangsbedingungen und Solver-Einstellungen bestätigt, dass nichts übersehen wurde. Durch die Überprüfung einer dokumentierten Zusammenfassung der Modelleinstellungen stellen die Teams sicher, dass jedes Detail mit dem Hardware-Testplan übereinstimmt. Gut kommentierte Modelle und klare Notizen helfen auch bei der Übergabe, sodass jeder, der den Test durchführt, genau weiß, wie alles eingerichtet ist.

Jeder dieser Überprüfungsschritte bietet die Möglichkeit, Unstimmigkeiten zu erkennen, bevor auch nur ein einziger Draht angeschlossen wird. Das Ergebnis ist ein Modell, das aus jedem Blickwinkel geprüft wurde und den Ingenieuren das nötige Vertrauen gibt, um mit Hardware-in-the-Loop-Experimenten fortzufahren.

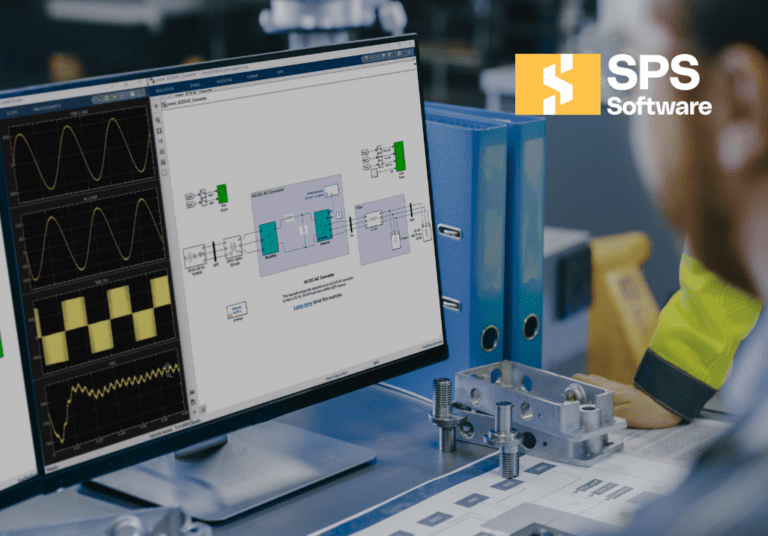

SPS SOFTWARE integrierter Modellvorbereitungs-Workflow

Als letzten Schritt verbinden die Integrationsteams Design und Test mit einem einheitlichen Modell, um Übersetzungsfehler zu vermeiden. Durch diesen integrierten Ansatz korrelieren die Ergebnisse über verschiedene Kontexte hinweg, sodass sich die Ingenieure auf die Interpretation der Ergebnisse konzentrieren können, anstatt Tools abzustimmen. SPS SOFTWARE bietet eine solche Plattform: Sie nutzt offene, transparente Komponentenbibliotheken und eine direkte MATLAB/Simulink-Integration, sodass das Modell, das Sie in der Simulation validieren, zum Code wird, der auf dem Echtzeitsystem ausgeführt wird. Dies eliminiert redundante Arbeit und hilft Ihrem Team, sich auf die Ergebnisse statt auf die Tool-Konfiguration zu konzentrieren. Das Ergebnis sind schnellere Iterationen und mehr Vertrauen in die Endergebnisse.