Principaux enseignements

- Une préparation rigoureuse donne aux équipes d'intégration l'assurance que les modèles fonctionneront de manière cohérente une fois connectés au matériel, ce qui réduit les surprises coûteuses et les retards.

- Des composants physiques précis constituent la base des tests matériels qui reflètent la manière dont les systèmes réagissent sous contrainte.

- Les étapes d'optimisation en temps réel aident les modèles à respecter les délais d'exécution fixes afin que vous puissiez effectuer des tests matériels sans dépassement ni instabilité.

- Une planification précoce de l'interface minimise les retouches en garantissant que chaque signal, canal, unité et mise à l'échelle est aligné avant que le système n'atteigne le banc d'essai.

- Des pratiques d'examen approfondi offrent aux équipes une méthode structurée pour valider les comportements, le calendrier et les hypothèses avant de commencer les essais matériels.

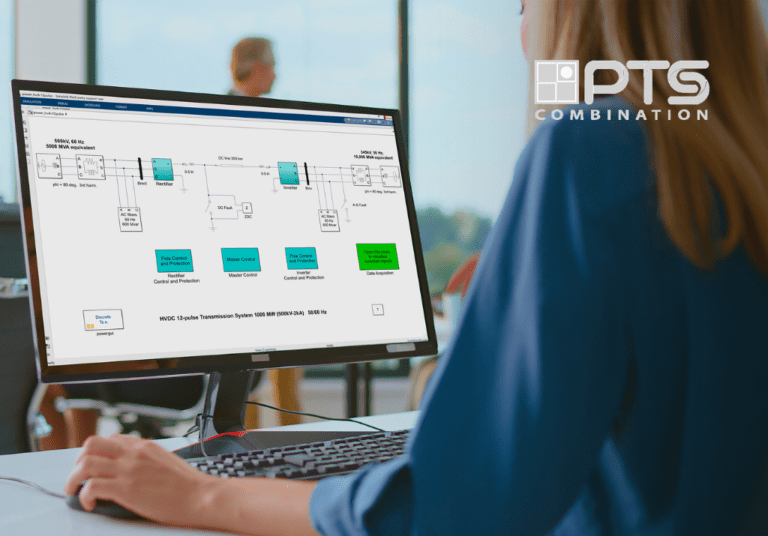

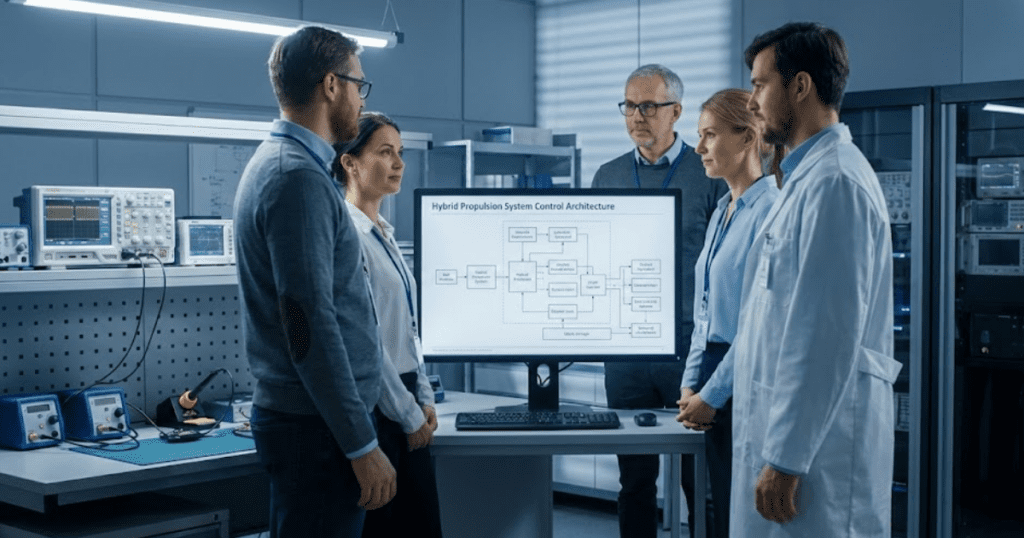

Un seul modèle de simulation incorrect peut compromettre l'ensemble d'un plan de test matériel. Les équipes d'intégration constatent souvent que des modèles qui fonctionnent parfaitement sur un ordinateur de bureau se comportent de manière imprévisible dans des conditions en temps réel. Nous avons vu des projets bloqués lorsqu'un modèle de contrôleur ne parvient soudainement plus à respecter les délais sur le matériel cible ou lorsque les interfaces de signal ne correspondent pas au banc physique. Sans une préparation rigoureuse, les tests HIL (Hardware-in-the-Loop) donnent des résultats peu fiables, voire des défaillances critiques. Par exemple, les laboratoires en temps réel modernes peuvent simuler des réseaux électriques complexes comportant environ 10 000 nœuds, ce qui signifie que même une petite erreur de modélisation peut avoir des répercussions en cascade sur l'ensemble du système. Une préparation rigoureuse des modèles permet de résoudre ces problèmes : vérification de la fidélité, optimisation des performances et double vérification des interfaces en amont. Cela se traduit par des tests plus sûrs, des itérations plus rapides et un niveau de confiance plus élevé dans les résultats.

Des modèles précis évitent les surprises lors des tests matériels

Une modélisation physique précise est la base d'un test matériel fiable. Si un modèle utilise des composants trop simplifiés ou des signaux fixes, son comportement peut s'écarter du système réel testé. Les ingénieurs doivent s'assurer que chaque composant est basé sur la physique et les paramètres du système réel. Par exemple, négliger les pertes dans un convertisseur de puissance ou idéaliser les réponses des capteurs peut entraîner des incohérences qui n'apparaissent que lorsque le modèle est connecté à du matériel réel. Ce type de divergence oblige les équipes à rechercher les problèmes en dehors de la simulation, ce qui leur fait perdre un temps précieux.

Par exemple, les laboratoires en temps réel tels que le simulateur de réseau d'Oak Ridge peuvent traiter environ 10 000 nœuds , et une plateforme open source a même simulé 24 000 électrons en temps réel. Une telle échelle souligne le fait que, dans les simulations à grande échelle, même les erreurs mineures peuvent se multiplier. Les équipes doivent calibrer les modèles par rapport aux mesures et valider leur comportement dans toutes les conditions prévues afin que la simulation reflète fidèlement la réalité. Lorsque chaque composant est précis et transparent, les ingénieurs peuvent ajuster les paramètres à la volée et être assurés que les modifications produisent des résultats significatifs.

« Les équipes doivent calibrer les modèles par rapport aux mesures et valider leur comportement dans toutes les conditions prévues afin que la simulation reflète fidèlement la réalité. »

Les performances en temps réel nécessitent un modèle optimisé.

Même un modèle précis échouera s'il ne peut pas fonctionner assez rapidement en temps réel. Les ingénieurs doivent rationaliser les modèles afin que chaque calcul soit adapté à la fréquence d'horloge du matériel. Les stratégies courantes consistent à utiliser des solveurs à pas fixes et des sous-systèmes synchrones, à fusionner ou à aplatir les blocs hiérarchiques, et à supprimer ou simplifier les éléments lourds en termes de calcul. Par exemple, un modèle de convertisseur multidomaine peut exécuter la physique électrique par pas de 10 µs et les effets thermiques par pas de 100 µs, ce qui oblige à choisir soigneusement le timing.

- Solveur et taille des pas : définissez le type de solveur et la taille des pas de temps afin qu'ils correspondent à la fréquence du matériel en temps réel, garantissant ainsi une exécution déterministe et évitant l'incertitude liée aux pas variables.

- Simplifiez les modèles : supprimez les champs d'enregistrement, les blocs de diagnostic et toutes les boucles algébriques ou fonctions rares qui ralentissent l'exécution.

- Aplatir et optimiser les sous-systèmes : fusionner les blocs en cascade et utiliser des options de génération de code efficaces pour réduire la charge de calcul.

- Types de données et virgule fixe : sélectionnez les types de données (par exemple, virgule fixe) qui conviennent à la cible en temps réel et minimisent les conversions de types coûteuses.

- Génération et déploiement de code : générez du code C/HDL optimisé pour la plateforme temps réel, compilez-le et corrigez tout problème de génération de code avant le test.

- Chemins de signaux allégés : n'incluez que les signaux et calculs nécessaires dans la boucle d'exécution afin de réduire la charge et de préserver la synchronisation.

Ces étapes permettent de transformer un modèle de conception en un modèle qui répond aux contraintes en temps réel. Il en résulte moins de délais non respectés et un timing d'exécution reproductible. Dans l'ensemble, les modèles optimisés garantissent que le matériel peut calculer chaque étape à temps, évitant ainsi les instabilités numériques et les dépassements.

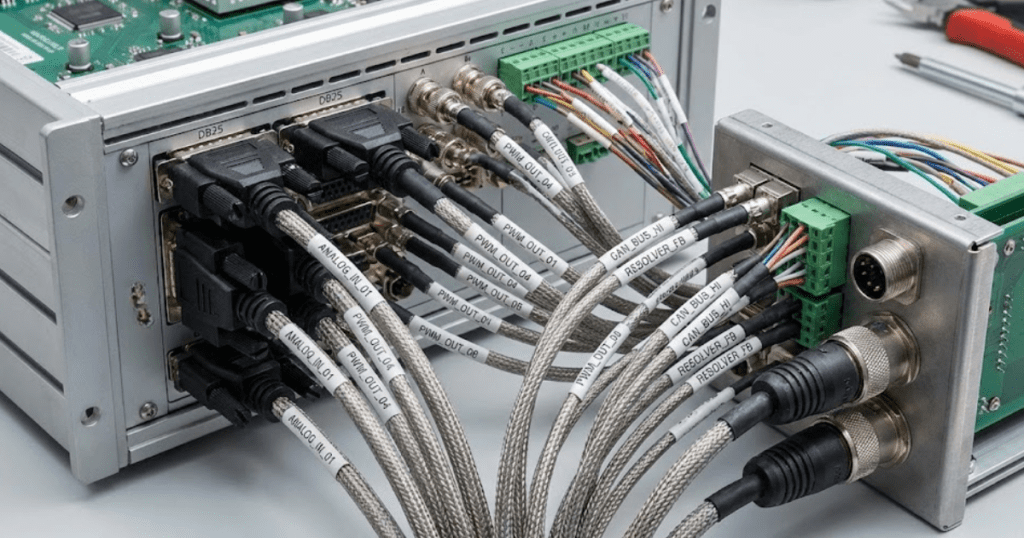

Une planification précoce de l'interface permet d'éviter les contretemps liés à l'intégration.

Les tests matériels échouent souvent en raison de signaux incompatibles ou d'exigences d'E/S négligées. Au début du projet, les équipes doivent planifier chaque interface entre le modèle et l'équipement de test. Cela implique de définir chaque canal d'entrée et de sortie, ses unités, sa plage et le type de données attendu avant de construire la configuration HIL. La définition précoce de ces spécifications d'interface permet d'éviter les surprises, telles qu'un signal de tension branché sur le mauvais amplificateur ou une incompatibilité de synchronisation sur un bus de communication. Il est utile de créer dès le début une documentation de tous les canaux et de tous les mappages de signaux.

Les équipes vérifient également la cohérence des unités et de la mise à l'échelle. Elles s'assurent que chaque signal de modèle utilise les mêmes unités que celles attendues par le matériel et que les formats numériques (tels que les plages de bits ADC ou les protocoles de communication) correspondent. Par exemple, le mappage des sorties des blocs Simulink aux canaux matériels et leur vérification à l'aide de signaux de test simples permettent de détecter rapidement les problèmes d'alignement. La documentation des affectations de canaux, des plages de valeurs attendues et des mappages de connecteurs devient une liste de contrôle concrète pour la phase d'intégration. Dans la pratique, le fait de traiter la configuration de l'interface comme une tâche parallèle à la modélisation permet de réduire de plusieurs jours le temps de débogage. Au moment de l'intégration, les équipes peuvent connecter le modèle en toute confiance, en se concentrant sur les fonctionnalités plutôt que sur la recherche d'incohérences.

Les révisions approfondies des modèles constituent la dernière vérification avant les tests matériels.

« Un seul modèle de simulation incorrect peut compromettre l'ensemble d'un plan de test matériel. »

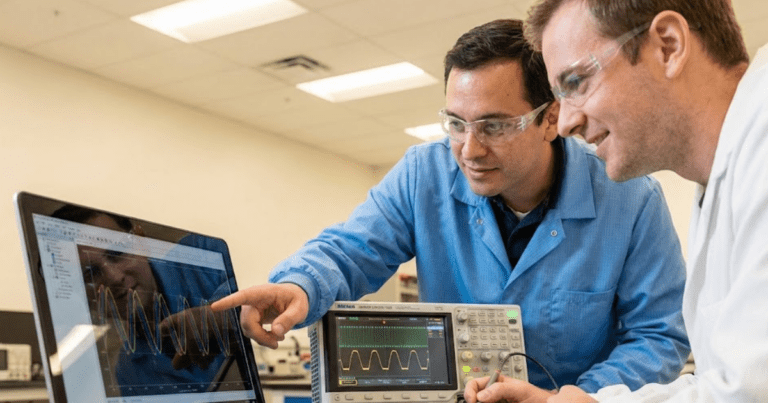

Vérifier le comportement des composants

Les ingénieurs vérifient chaque composant en le testant séparément, si possible. Par exemple, ils peuvent piloter un capteur simulé avec une forme d'onde d'entrée connue et s'assurer que la sortie correspond aux données théoriques ou expérimentales. La vérification des cas limites et des réponses au bruit des capteurs permet de détecter rapidement les problèmes de modélisation. Le code personnalisé et les tables de consultation sont également examinés à ce stade, afin de s'assurer que chaque bloc fonctionne comme prévu et que ses sorties correspondent aux attentes. Ces tests au niveau des composants permettent de détecter toute erreur dans son contexte et d'éviter qu'elle ne compromette les tests à plus grande échelle.

Tester les scénarios limites

Un examen approfondi couvre également les conditions anormales. Les ingénieurs simulent des scénarios de défaillance, des entrées extrêmes et des conditions limites pour vérifier si la réponse du modèle reste réaliste. Par exemple, ils peuvent simuler une perte soudaine d'alimentation ou une lecture nulle du capteur afin de valider la logique de protection et la robustesse du contrôleur. Le fait de repérer les comportements irréalistes ou instables dans ces simulations permet d'éviter les surprises lors des tests réels. Ces tests de résistance servent de contrôle de cohérence, garantissant que les hypothèses cachées dans le modèle ne sont pas remises en cause dans des conditions extrêmes.

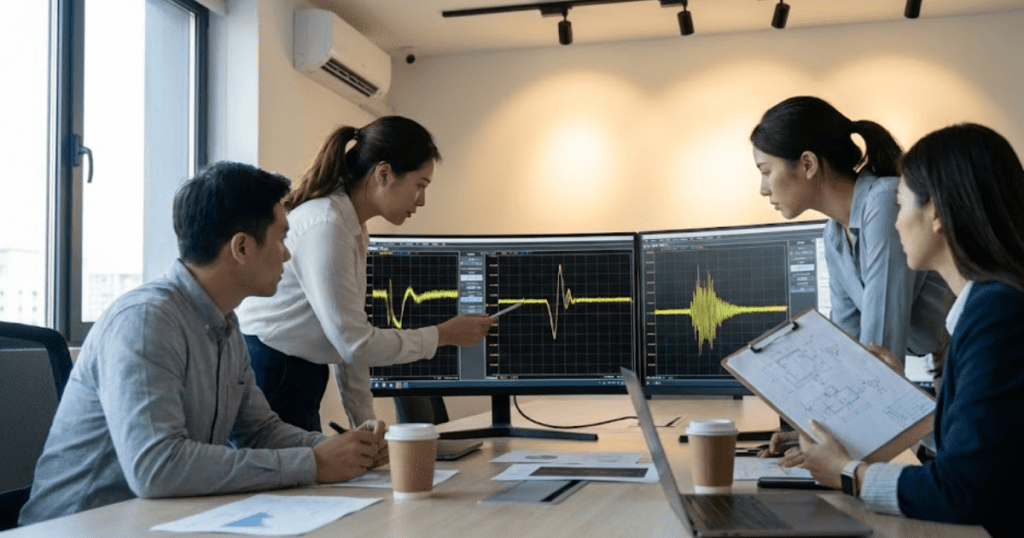

Vérifier les performances et le timing

Au cours de la révision, les équipes confirment que l'exécution du modèle se situe dans des limites acceptables sur le matériel cible. Cela inclut la vérification que le modèle respecte le temps d'échantillonnage prévu sans dépassement. Un simple test de compilation et d'exécution sur la plate-forme en temps réel révèle si une tâche prend trop de temps. Les ingénieurs surveillent les délais non respectés ou les avertissements du solveur et s'assurent que toutes les E/S matérielles (comme les blocs PWM ou ADC) utilisent le timing correct. Le fait de détecter ces goulots d'étranglement dès maintenant permet d'éviter des problèmes d'intégration ultérieurs sur le banc d'essai réel.

Documenter les hypothèses et les interfaces

Enfin, la révision d'un modèle comprend la documentation. Les ingénieurs récapitulent toutes les hypothèses importantes, les valeurs des paramètres et les mappages d'interface. Une liste récapitulative des variables d'état, des conditions initiales et des paramètres du solveur permet de s'assurer que rien n'a été oublié. En examinant un résumé documenté des paramètres du modèle, les équipes s'assurent que chaque détail correspond au plan de test matériel. Des modèles bien commentés et des notes claires facilitent également la transmission, de sorte que toute personne effectuant le test sait exactement comment tout est configuré.

Chacune de ces étapes de révision est l'occasion de détecter les anomalies avant même que le moindre câble ne soit branché. Le résultat est un modèle qui a été vérifié sous tous les angles, ce qui donne aux ingénieurs la confiance nécessaire pour passer aux expériences de simulation en boucle fermée.

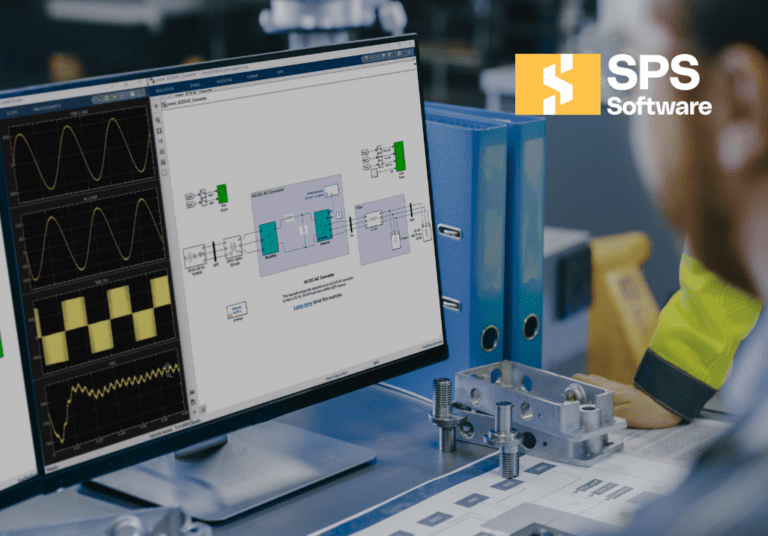

Workflow intégré de préparation des modèles SPS SOFTWARE

Enfin, les équipes d'intégration relient la conception et les tests à l'aide d'un modèle cohérent afin d'éliminer les erreurs de traduction. Grâce à cette approche intégrée, les résultats sont corrélés entre les différents contextes, et les ingénieurs peuvent se concentrer sur l'interprétation des résultats plutôt que sur la réconciliation des outils. SPS SOFTWARE propose ce type de plateforme : elle utilise des bibliothèques de composants ouvertes et transparentes et une intégration directe MATLAB/Simulink afin que le modèle que vous validez dans la simulation devienne le code exécuté sur le système en temps réel. Cela élimine les tâches redondantes et aide votre équipe à se concentrer sur les résultats plutôt que sur la configuration des outils. Il en résulte des itérations plus rapides et une plus grande confiance dans les résultats finaux.