Key Takeaways

- Switching losses come from voltage and current overlap during finite transitions, and high frequency turns small event energies into significant heat.

- Datasheet energies, thermal impedance, and junction temperature feedback belong in the same model if you want reliable converter thermal results.

- Gate resistance, layout parasitics, and transient thermal swings often set the safe operating limit before heatsink size does.

Switching losses decide junction temperature sooner than most heatsink calculations admit.

A field failure survey summarized in the IEEE reliability literature found that power semiconductor devices accounted for 31% of reported failures in power electronic systems. That matters because thermal stress is rarely created by conduction loss alone in modern converters. Once your switching frequency climbs, each turn on and turn off event adds a small burst of energy that turns straight into heat. If you only size copper, silicon area, and heatsinks around average current, you’ll miss the part of the loss budget that often sets the safe operating limit.

“That overlap creates energy loss in every cycle.”

Switching losses decide junction temperature sooner than most heatsink calculations admit.

A field failure survey summarized in the IEEE reliability literature found that power semiconductor devices accounted for 31% of reported failures in power electronic systems. That matters because thermal stress is rarely created by conduction loss alone in modern converters. Once your switching frequency climbs, each turn on and turn off event adds a small burst of energy that turns straight into heat. If you only size copper, silicon area, and heatsinks around average current, you’ll miss the part of the loss budget that often sets the safe operating limit.

Switching loss starts during finite voltage current overlap

Switching loss begins when drain to source voltage and drain current exist at the same time during turn on and turn off. A MOSFET is not an ideal switch that jumps from fully blocking to fully conducting. Gate charge, parasitic capacitances, and circuit inductance stretch the transition. That overlap creates energy loss in every cycle.

A hard switched half bridge makes this easy to picture. During turn on, the current rises while the device still supports much of the bus voltage. During turn off, the current is still flowing while voltage climbs again. The product of voltage and current during those short intervals creates switching losses in MOSFET devices, even if the on state resistance is low and the conduction interval looks efficient.

You can’t treat those intervals as rounding errors once frequency rises. A converter running at 20 kHz may tolerate a rough estimate early in design, but a design at 100 kHz or 250 kHz will turn a few microjoules per edge into watts of heat. That’s why accurate thermal modelling starts with the overlap event, not with the heatsink.

A simple switching loss formula works only for screening

The common screening formula estimates switching power from the overlap triangle during turn on and turn off. You multiply bus voltage, load current, and transition time, then scale that event energy with switching frequency. It gives a quick first pass. It will not capture the full behaviour of an actual converter.

You’ll often see the estimate written as Psw ≈ 0.5 × V × I × (tr + tf) × fs. That form is useful when you’re comparing candidate devices for the same bus voltage and current. A 400 V converter switching 20 A with combined rise and fall time of 80 ns at 100 kHz produces a rough estimate near 32 W. That number is helpful for screening, but it hides reverse recovery, output capacitance loss, gate loop effects, and load current variation.

The formula also assumes linear transitions and constant current. Actual waveforms rarely behave that cleanly. Parasitic inductance can slow one edge and sharpen the other. A clamped inductive load will produce a different switching shape than a resonant leg. Use the simple formula to reject weak options early, then move to measured or simulated energy per event before you trust a thermal result.

Datasheet curves account for voltage current temperature dependence

Datasheet switching energy curves are more useful than the simple overlap formula because they include how the device behaves under tested voltage, current, gate resistance, and temperature conditions. Those curves convert switching losses in MOSFET parts from guesswork into a parameterized estimate. They still need correction for your exact circuit.

A typical datasheet gives turn on energy and turn off energy at a stated bus voltage, current, and gate resistance. If your converter runs at half the tested current, you can’t assume the energy will scale perfectly in half. The output capacitance discharge, reverse recovery of the companion diode, and Miller plateau behaviour distort that scaling. Junction temperature also matters because carrier mobility, threshold shift, and parasitic behaviour all change with heat.

When you read those plots, treat test conditions as part of the number. A curve measured at 25°C with a 10 Ω gate resistor will understate loss for a converter that actually runs near 100°C with a 22 Ω resistor. This is where you stop thinking about one MOSFET value and start thinking about a switching system.

Average power follows event energy times switching frequency

Average switching power comes from the sum of turn-on and turn-off energy per event multiplied by switching frequency. That relationship is the most reliable bridge between waveform detail and thermal design. Once you know event energy under your conditions, the thermal model has a meaningful heat source to solve.

The practical form is Psw = (Eon + Eoff) × fs. If one device dissipates 120 µJ at turn-on and 90 µJ at turn-off, a 100 kHz operating point gives 21 W of switching power. Double the frequency and that term doubles too, even when load current and duty ratio stay the same. That linear link is why high-frequency designs often become thermal problems before they become current problems.

The checkpoint below helps separate the inputs that deserve attention first when you calculate MOSFET switching losses for simulation and thermal sizing.

| Input or check | What it tells you |

|---|---|

| Bus voltage under worst operating condition | The highest applied voltage will stretch the switching energy and usually sets the harder thermal case. |

| Load current at the instant of switching | The current during each edge matters more than average output current when you estimate event energy. |

| Turn on and turn off energy from matched test conditions | Using energies measured near your gate resistance and temperature avoids a large error in average power. |

| Switching frequency across the operating range | A modest increase in frequency raises switching power in direct proportion and often moves the thermal limit first. |

| Conduction loss calculated at hot resistance | Hot on state resistance keeps the total loss budget honest once switching heat has already raised junction temperature. |

| Dead time and diode recovery behaviour | These details often explain why measured loss is higher than a clean energy sum from a datasheet curve. |

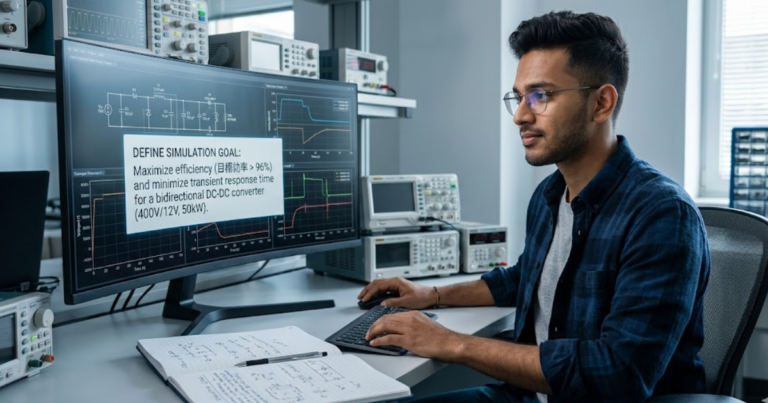

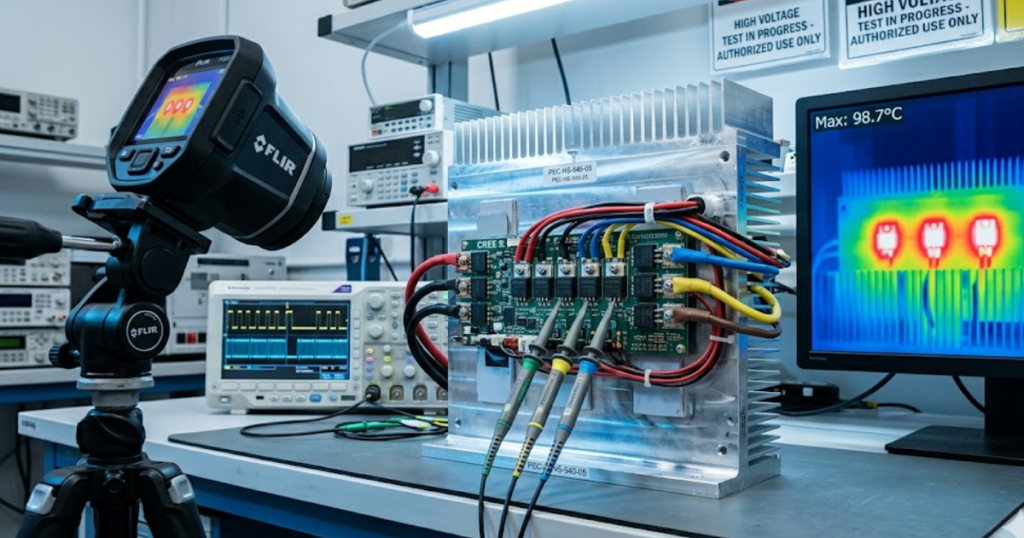

Electrothermal simulation links switching events to junction temperature

Electrothermal simulation turns electrical loss into junction temperature by coupling a loss model with a thermal network. That link matters because device temperature shifts the same parameters that created the loss. You’re solving a loop, not a one way calculation. A static estimate will miss that feedback.

A useful converter model starts with electrical waveforms or event energies, then feeds those losses into a thermal impedance path from junction to case, case to sink, and sink to ambient. The updated junction temperature then adjusts on state resistance, threshold behaviour, and switching energy for the next step. That is how you move from a spreadsheet number to a believable operating point. SPS SOFTWARE fits this workflow when you need transparent electrothermal blocks that you can inspect and adjust instead of accepting a hidden thermal assumption.

The value of this approach shows up when operating points shift. A converter that looks safe at nominal load may cross a thermal limit during light load high-frequency operation, where conduction loss falls but switching loss still stays high. Once you model that loop, you’ll see why thermal effects belong inside converter simulation rather than after it.

“You’re not only tracking the average hot spot. You’re tracking how far and how often the junction moves.”

Transient impedance shapes temperature rise more than steady averages

Transient thermal impedance tells you how quickly a device heats during pulsed loss, and that matters more than steady thermal resistance when switching power is uneven over time. Junction temperature follows pulses, bursts, and duty cycles with delay. Average dissipation alone will hide those peaks. Short overloads can still push silicon past a safe temperature.

A motor drive shows this clearly during acceleration. Current rises for a few hundred milliseconds, switching energy increases, and the junction responds much faster than the heatsink. The case may still look cool while the die has already reached a dangerous peak. A commonly used power cycling data set showed lifetime dropping from about 10 million cycles at a 60 K junction swing to about 1 million cycles at 100 K, which shows why transient temperature swing matters so much.

That is why thermal modelling improves power converter reliability. You’re not only tracking the average hot spot. You’re tracking how far and how often the junction moves. Packaging fatigue, solder stress, and bond wire wear respond to those swings, so transient impedance belongs in the model from the start.

Gate resistance tuning sets the first switching loss tradeoff

Gate resistance is often the first knob you turn because it directly alters switching speed, voltage overshoot, ringing, and electromagnetic noise. Lower resistance reduces overlap time and cuts switching loss. Higher resistance softens edges and can protect against overshoot. You won’t get the best result from either extreme.

A synchronous buck converter with a very small gate resistor will switch quickly and run cooler in the silicon, yet the drain waveform can overshoot enough to stress the device and raise noise. A much larger resistor will calm the edge, but transition time will lengthen and switching power will climb. The right value depends on package inductance, gate driver strength, and layout quality as much as the MOSFET itself.

- Use a smaller gate resistor when overlap loss is the main thermal limit.

- Use a larger gate resistor when overshoot or ringing threatens device margin.

- Check turn on and turn off separately because the best values often differ.

- Measure at hot conditions because edge speed shifts with junction temperature.

- Retune after layout changes because parasitic inductance changes the result.

That tradeoff is why reducing switching losses in MOSFET-based converters is rarely a single part choice. Gate drive settings, loop inductance, and thermal margin all move as a group. You’ll get a better answer from measured waveforms and a coupled model than from a nominal resistor value copied from a reference design.

Heatsink sizing fails when switching loss is undercounted

A heatsink calculation fails when the loss number feeding it ignores switching energy, temperature feedback, or transient peaks. The sink can be perfectly sized for the wrong power input and still produce an overheated converter. Good thermal design starts with disciplined loss modelling, then uses the heatsink as the last step rather than the first guess.

A common failure path looks harmless on paper. You choose a low resistance device, estimate conduction loss at room temperature, and pick a sink that seems to hold the case comfortably below its limit. Bench tests then show the junction climbing during high-frequency operation because switching losses in MOSFET devices were understated. That missing heat raises junction temperature, which raises on-state resistance, which pushes total loss higher again. The error compounds rather than staying fixed.

SPS SOFTWARE is most useful at this stage when you want the electrical and thermal assumptions kept visible enough to challenge. That habit will give you better converter margins than any oversized heatsink alone. Careful modelling won’t remove tradeoffs, but it will show you which ones are worth paying for and which ones are just hidden loss.